1月22日,由逻辑比特科技(Logical Qubit Technology)核心成员参与的联合科研团队在全球顶级学术期刊Nature Physics发表论文“Demonstration of low-overhead quantum error correction codes”,在具有长程耦合器的超导量子处理器上,全球首次实现了高编码率Bivariate bicycle codes的量子纠错实验演示。

量子纠错技术新方向

实现大规模容错量子计算的核心,在于通过量子纠错技术显著降低逻辑量子比特的错误率。在超导量子计算领域,表面码(Surface Code)凭借对硬件友好的近邻耦合需求,长期占据着容错量子计算的主流地位,谷歌是表面码纠错最具代表性的公司。然而,表面码的低编码率导致其在扩展道路上面临着高昂的硬件资源开销。如何在提升纠错性能的同时降低硬件资源成本成为新的探索思路。

在这一背景下,高编码率的量子低密度奇偶校验码(qLDPC)被视为降低资源开销的重要路线。2023年,Bravyi领导的IBM团队提出了Bivariate Bicycle Code(BB Code)。这种新型纠错码在传统表面码仅关联四个相邻比特的基础上,巧妙地引入了两个经过精心选择的“非局域长程”连接。其理论模拟表明,在所采用的噪声模型与性能指标设定下,BB Code仅需表面码约十分之一的物理比特开销即可达到同等纠错性能,为低成本量子纠错指明了新方向。

创新芯片设计和制备攻克工程难题

尽管BB Code理论优越,但将其从图纸落实到硬件实施却面临极大的挑战。要在二维平面的量子芯片上构建非局域的长程连接,且要并行地在这些复杂的长程耦合上实现高保真度量子门,其工程实现的难度明显高于仅需近邻连接的表面码。

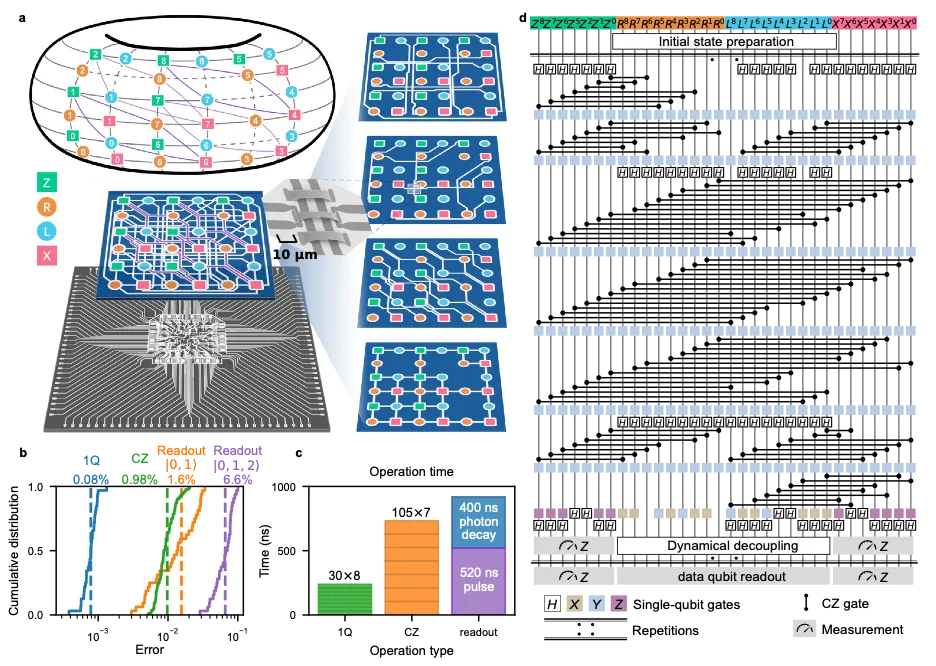

针对这一难题,逻辑比特科技核心成员参与设计了“昆仑(Kunlun)”32比特高连通超导量子芯片。该芯片在二维近邻连接的基础上,引入了额外的长程可调耦合结构,以支持BB Code所需的高连通度和非局域稳定子测量。

为攻克长程耦合带来的布线交叉与寄生耦合等工程难题,团队在芯片制造工艺上进行了针对性优化,在长程耦合器上引入了空气桥(air bridges)跨越结构。这一关键工艺有效解决了高连通超导芯片面临的复杂拓扑布线问题,为在长程耦合器上实现高保真并行操控提供了重要支撑。

实验标定结果显示,“昆仑”量子处理器的单比特门与两比特门的平均并行保真度分别达到 99.95% 和 99.22%。

昆仑量子处理器架构图以及BB Code的非局域和稳定子提取线路

基于“昆仑”量子处理器,团队在实验中演示了两种BB Code方案:[[18,4,4]]码和[[18,6,3]]码。前者利用18个数据比特编码4个距离为4的逻辑比特,后者编码了6个距离为3的逻辑比特。通过执行高效的非局域稳定子提取线路,团队成功演示了多轮量子纠错。

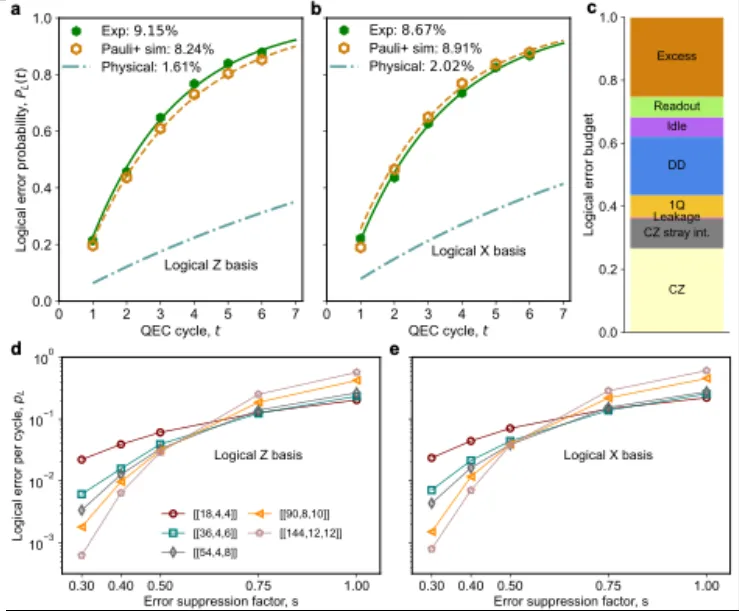

实验结果表明,[[18,4,4]]码和[[18,6,3]]码的平均逻辑错误率(按每轮、每逻辑比特统计)分别为8.91%和7.77%。此外,研究团队的数值模拟预测,在所采用的噪声模型与解码设定下,若能将当前芯片的物理操作错误率降低至现有水平的一半,则可跨越BB Code的纠错阈值,为未来突破盈亏平衡点(即逻辑比特寿命超越物理比特寿命)提供重要基础。

[[18,4,4]]BB Code的部分实验结果图

可纠错量子芯片是通用量子计算机的基石

量子纠错是实现大规模容错量子计算的必经之路。目前,大众对量子计算的认识更多来自对量子计算机的直观视觉感受,而一台完整的超导量子计算机则包含量子芯片、量子测控系统、量子射频系统以及量子软件及算法等重要组成部分。其中,芯片又是量子计算机绝对不能缺少的基石,而可纠错量子芯片又是决定未来通用量子计算战略竞争的关键胜负手。

可纠错量子芯片是一个系统化、工程化的问题,不单单考验芯片设计和制备的能力,同样也考验量子测控、射频、软件等协同适配的能力。正因如此,逻辑比特科技团队从一开始就锚定“技术驱动+工程创新”的叠加能力,立足浙大超导量子计算实验室在芯片设计和制备领域的技术积累,在推进表面码纠错的基础上探索和验证更加高效的纠错路线。与此同时,不断提升自身工程化能力,自主掌握从芯片、射频、测控到量子计算机整机的核心技术以及工程化能力。以务实的方式加速量子计算时代的到来。